PDI1394P23BD

2 PORT PHY I/O Controller Interface IC IEEE1394A

-

製造商零件號 # : PDI1394P23BD

-

包裝/封裝: SOT-314

-

產品分類 : Controllers

品質保證

品質保證

從我們的供應鍊網路採購的所有零件都經過嚴格的進貨檢驗流程。 這種細緻的檢查可確保客戶收到的零件是正品並符合要求的標準。 此外,我們還保存這些檢查的詳細記錄,以確保整個供應鏈的透明度和可追溯性。

認證

我們已成功獲得各項認證標準,並建立了自己的專業檢測實驗室。 這確保了我們向客戶提供的每件產品都符合最高的品質標準。 我們遵守嚴格的測試協議,以保持我們產品的一致性和準確性。 為了確保我們的產品是原裝正品,我們還與信譽良好的第三方檢測機構合作進行嚴格的品質測試。 我們對品質的承諾延伸到滿足行業、法律、監管和 ISO 9001:2015 的要求。

運輸與付款

運輸與付款

關於運送

我們通常會在幾個工作日內通過可靠的運輸公司(例如 FedEx、SF、UPS 或 DHL)運送訂單。 我們還支持其他運輸方式。 如果您想詢問具體的運輸細節或費用,請隨時與我們聯繫。

關於付款

我們接受多種支付方式,包括VISA、MasterCard、銀聯、西聯、PayPal等渠道。

如果您有特定的付款方式或想詢問費率和其他詳細信息,請隨時與我們聯繫。

電匯

Paypal

信用卡

西聯匯款

速匯金

服務與包裝

服務與包裝

About After Sales Service

All Parts Extended Quality Guarantee

自發貨之日起 90 天內發起申請。

與我們的工作人員確認退貨或換貨。

保持貨物收到時的原始狀態。

最後請注意,退貨或換貨的資格取決於對退貨商品實際狀況的評估。 在完成退貨或換貨流程之前,我們將評估收到的貨物。 如果您對退貨或換貨有任何疑問或需要進一步幫助,請隨時通過以下方式聯絡我們: [email protected]

關於包裝

在包裝方面,我們的產品均精心包裝在防靜電袋中,以提供ESD防靜電保護。 外包裝堅固耐用且閉合牢固。 我們支持各種包裝方法,例如捲帶式、切帶式、管式或託盤式。

例子

捲帶式

剪膠帶

管或託盤

PDI1394P23BD 數據表

目前的價格方案正在編制中。請聯絡我們的客戶服務團隊獲取最新的價格資訊。感謝您的理解和支援!

詳細說明

The PDI1394P23 provides the digital and analog transceiver functions needed to implement a two/one port node in a cable-based IEEE 1394–1995 and/or 1394a–2000 network. Each cable port incorporates two differential line transceivers. The transceivers include circuitry to monitor the line conditions as needed for determining connection status, for initialization and arbitration, and for packet reception and transmission. The PDI1394P23 is designed to interface with a Link Layer Controller (LLC), such as the PDI1394L40, or PDI1394L41.FEATURES• Fully supports provisions of IEEE 1394–1995 Standard for high performance serial bus and the P1394a–2000 Standard.1• Fully interoperable with Firewire and i.LINK implementations of the IEEE 1394 Standard.2• Full P1394a support includes: – Connection debounce – Arbitrated short reset – Multispeed concatenation – Arbitration acceleration – Fly-by concatenation – Port disable/suspend/resume• Provides two 1394a fully-compliant cable ports at 100/200/400 Mbps.• Fully compliant with Open HCI requirements• Interface to link-layer controller supports both low-cost bus-holder isolation and optional Annex J electrical isolation• Supports extended bias-handshake time for enhanced interoperability with camcorders• Data interface to link-layer controller through 2/4/8 parallel lines at 49.152 MHz• Register bits give software control of contender bit, power class bits, link active bit, and 1394a features• Cable ports monitor line conditions for active connection to remote node.• Separate cable bias (TPBIAS) for each port• Logic performs system initialization and arbitration functions• Encode and decode functions included for data-strobe bit level encoding• Incoming data resynchronized to local clock• Single 3.3 volt supply operation• Minimum VDD of 2.7 V for end-of-wire power-consuming devices• Interoperable with link-layer controllers using 3.3 V and 5 V supplies• Interoperable with other Physical Layers (PHYs) using 3.3 V and 5 V supplies• Node power class information signaling for system power management• Cable power presence monitoring• Power down features to conserve energy in battery-powered applications include: – Automatic device power down during suspend – Device power down terminal – Link interface disable via LPS – Inactive ports powered-down• While unpowered and connected to the bus, will not drive TPBIAS on a connected port, even if receiving incoming bias voltage on that port• Can be used as a one port PHY without the use of any extra external components• Low-cost 24.576 MHz crystal provides transmit, receive data at 100/200/400 Mbps, and link-layer controller clock at 49.152 MHz• Does not require external filter capacitors for PLL• LQFP package is function and pin compatible with the Texas Instruments TSB41LV02AE and TSB41AB2E 400 Mbps PHYs.

主要特徵

- Fully supports provisions of IEEE 1394–1995 Standard for high performance serial bus and the P1394a–2000 Standard.1

- Fully interoperable with Firewire and i.LINK implementations of the IEEE 1394 Standard.2

- Full P1394a support includes:

- – Connection debounce

- – Arbitrated short reset

- – Multispeed concatenation

- – Arbitration acceleration

- – Fly-by concatenation

- – Port disable/suspend/resume

- Provides two 1394a fully-compliant cable ports at 100/200/400 Mbps.

- Fully compliant with Open HCI requirements

- Interface to link-layer controller supports both low-cost bus-holder isolation and optional Annex J electrical isolation

- Supports extended bias-handshake time for enhanced interoperability with camcorders

- Data interface to link-layer controller through 2/4/8 parallel lines at 49.152 MHz

- Register bits give software control of contender bit, power class bits, link active bit, and 1394a features

- Cable ports monitor line conditions for active connection to remote node.

- Separate cable bias (TPBIAS) for each port

- Logic performs system initialization and arbitration functions

- Encode and decode functions included for data-strobe bit level encoding

- Incoming data resynchronized to local clock

- Single 3.3 volt supply operation

- Minimum VDD of 2.7 V for end-of-wire power-consuming devices

- Interoperable with link-layer controllers using 3.3 V and 5 V supplies

- Interoperable with other Physical Layers (PHYs) using 3.3 V and 5 V supplies

- Node power class information signaling for system power management

- Cable power presence monitoring

- Power down features to conserve energy in battery-powered applications include:

- – Automatic device power down during suspend

- – Device power down terminal

- – Link interface disable via LPS

- – Inactive ports powered-down

- While unpowered and connected to the bus, will not drive TPBIAS on a connected port, even if receiving incoming bias voltage on that port

- Can be used as a one port PHY without the use of any extra external components

- Low-cost 24.576 MHz crystal provides transmit, receive data at 100/200/400 Mbps, and link-layer controller clock at 49.152 MHz

- Does not require external filter capacitors for PLL

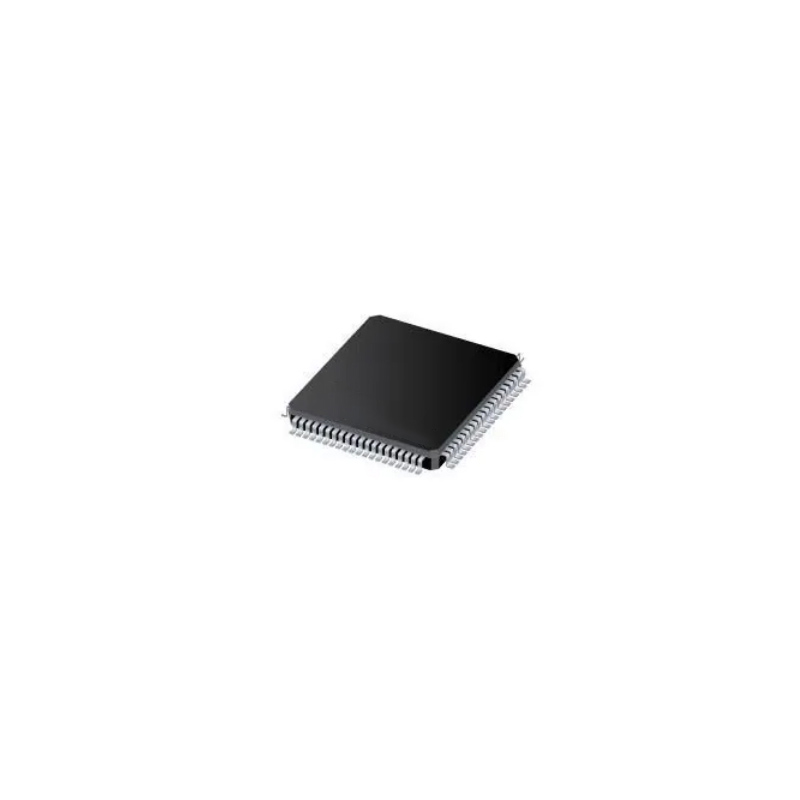

- LQFP package is function and pin compatible with the Texas Instruments TSB41LV02AE and TSB41AB2E 400 Mbps PHYs.

規格

以下是所選零件的基本參數,涉及零件的特性及其所屬類別。

| Product Category ! | I/O Controller Interface IC | Mounting Style | SMD/SMT |

| Package / Case | SOT-314 | Brand | NXP Semiconductors |

| Product Type ! | I/O Controller Interface IC | Factory Pack Quantity | 800 |

| Subcategory | Interface ICs |

數據表 PDF

數據表記錄了器件的特性、絕對最大額定值、應用等,這對於作為器件特定應用的整體指南大有裨益。

推薦零件

-

3,735 有存貨

貨物週期: 3~7 天

最小訂購量為 1

-

5,491 有存貨

貨物週期: 3~7 天

最小訂購量為 1

恭喜您提交成功

恭喜您提交成功

提交失敗

提交失敗